병렬 알고리즘 연구실(Parallel Algorithm Laboratory)

-

- Introduction

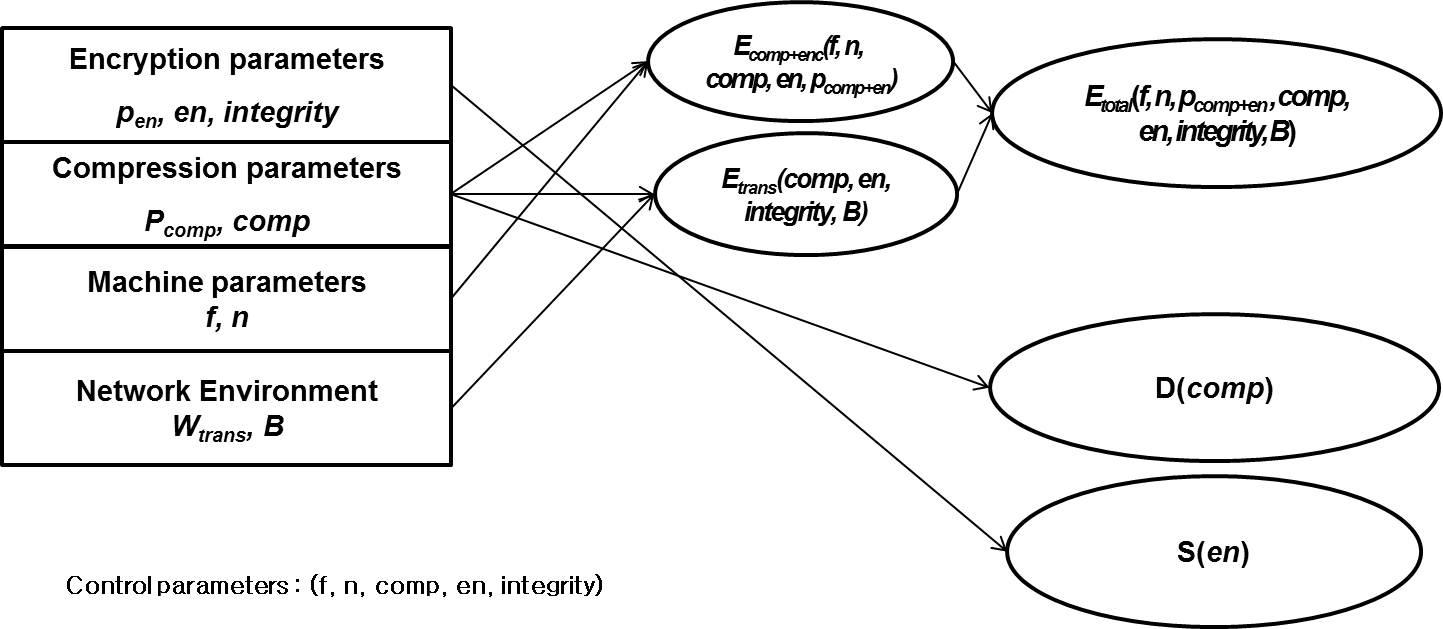

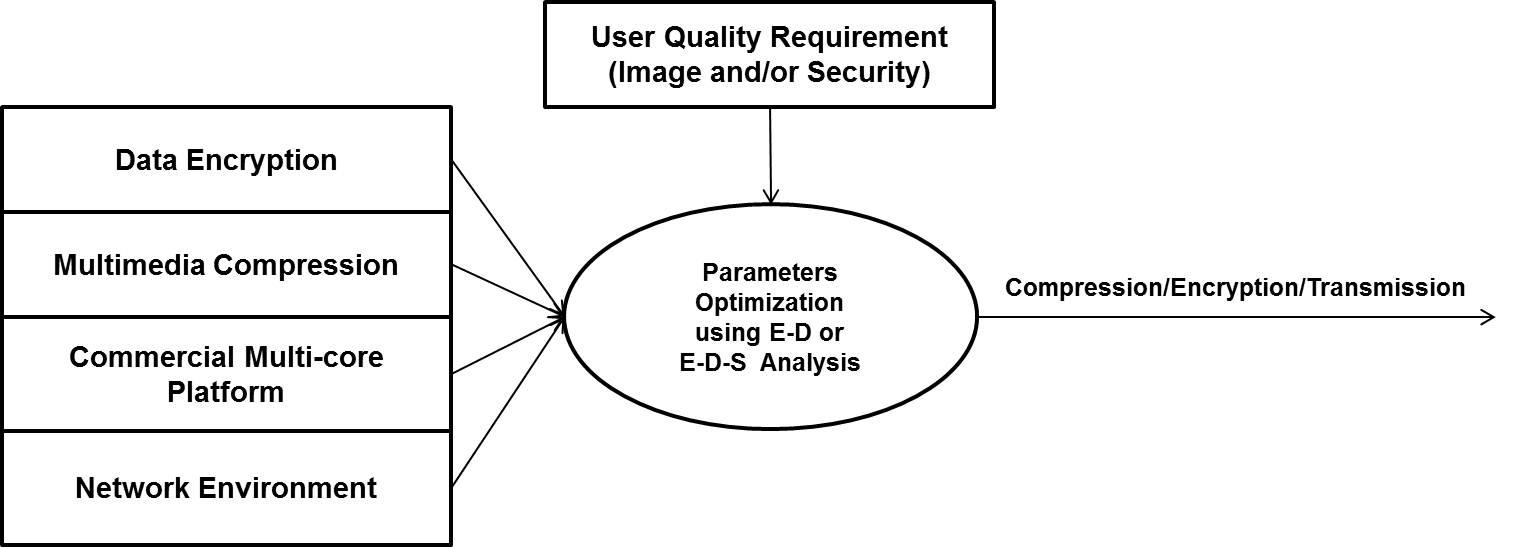

- To increase energy efficiency, the computer architectural approach controlling the frequency and/or the number of cores at hardware/software level, and the compression approach at algorithmic level have been proposed. In the computer architectural approach, there is a tradeoff between power consumption and execution time. That is, if we increase the frequency, the power consumption is increased while the execution time is decreased. In the image compression or information security, we can improve the performance efficiency at algorithmic level and/or derive the optimal applications parameter based on the tradeoff between the video/security quality and the energy consumption. We are researching the analysis of machine characteristics and parallel applications(multimedia/crypto/image processing algorithms) characteristics collectively, and thus improve the energy efficiency of compression using a commercial multi-core platform.

-

- Research Fields

-

- Computer Architecture

- Multi-core processor

- Symmetric/Asymmetric(Heterogeneous)

- Algorithms

- Parallel programming

- Load balancing

- Performance Indicator

- Reducing execution time

- Reducing energy consumption

- Applications Area

- Crypto algorithms

- Compression algorithms

- Image processing algorithms

-

-

- Current Projects

-

Project Title Sponsor Period Development of a Battery-driven Video Surveillance Algorithm based on the DVFS(Dynamic Voltage and Frequency Scaling) and Parallel Processing Techniques NRF 2009.05 ~ 2012.04 Development of a Multimedia Data Protection Algorithm based on the Characteristics of Compression and Cryptographic Techniques NRF 2009.09 ~ 2012.08 Development of Homenetwork Security Techniques MKE 2004.09 ~ 2012.12